# ASIC EVOLUTION FOR PARTICLE PHYSICS AND ASTROPHYSICS

Eduard ATKIN dep. of Electronics & ASIC Lab <u>evatkin@mephi.ru</u>

4nd International Conference on Particle Physics and Astrophysics (ICPPA-2018) 22-26 Oct 2018, Moscow

## Abstract

- Construction of the advanced megascience facilities, basing on advanced particle detector technologies, is closely connected with development of read-out electronics, having as a core element – Application Specific Integrated Circuit (ASIC)

- In order to reach limit specifications of multichannel detector setups a whole set of factors defines ASIC design. The chips should provide new level of functionality, fitting to a **new set of constraints and trade-offs** on technical specifications (like an integration scale, power consumption, speed, radiation hardness) as well as economic- and technology-related ones

- The talk presents overview of the state of the art and evolution in ASIC design for particle physics and astrophysics

# Aim is to present:

- Trends in ASIC design: history, state-of-the-art & what's next

- Transistor scaling

- Example projects of ASICs

- Conclusions & References

# Some main features of old ASICs (incl. LHC era)

- Many different Bipolar, Bi-CMOS and CMOS processes in the range of 350..

...250..130 nm from different foundries. No standardization at usage of both processes and design tools. Many different design teams with own strategy

- Integration scale for ASICs (typ.) 8-32 channels per chip, area of 1 sq.sm. max, no ADC in FEE, separate chips for analog and digital parts

- Rad-hard TID level up to few Mrads. Provided by both process and RHBD hardening

- Power consumption tens mW per channel

- 3-4 respins of prototyping before engineering run

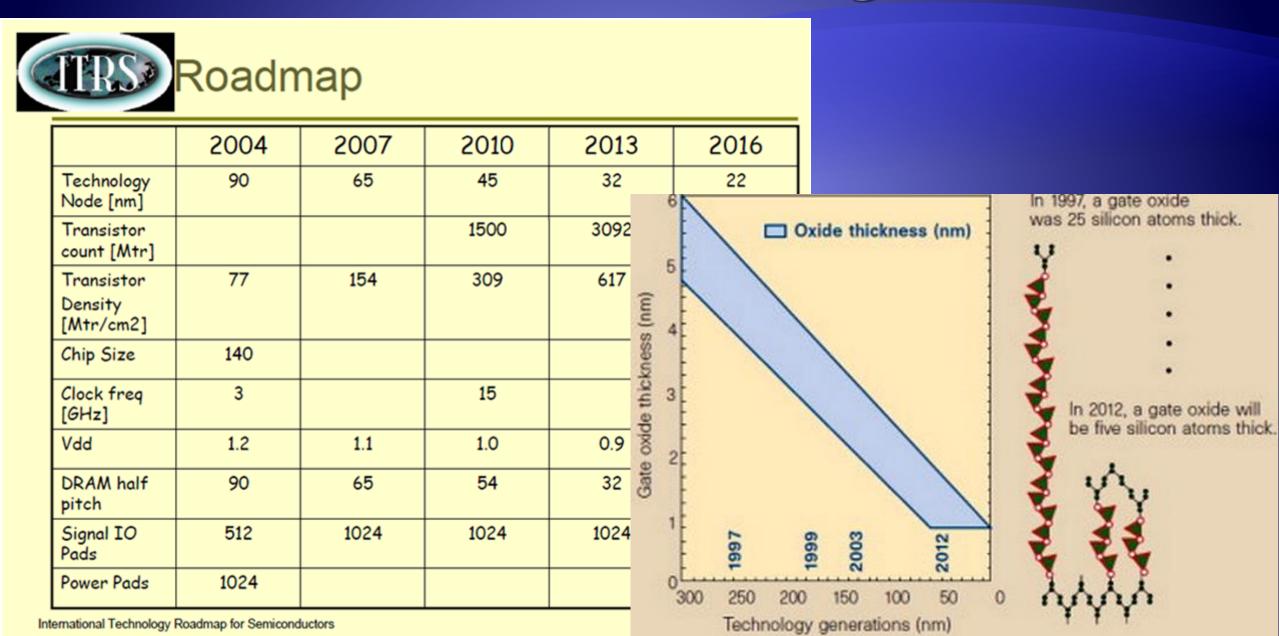

# **Transistor scaling**

# How could near future ASIC looks like? (1 of 3)

- Ideally based on hybrid technologies (at element, chip, package, board and finally system levels, incl. data transfer) to effectively reach a limit functionality

- System level efforts should take over the element level design. The accent at design is done at system (architectural) questions → SOCs (systems on a chip) dictate a mixed-signal character of design route

- The demanded number of ASIC wafers is small and can't interest a manufacturer (10<sup>6</sup> channels at ~100 chs/chip and ~1000 chips/wafer→ ~10 wafers only)

- Adaptation perspective ASIC for different projects as criterion of economic efficiency

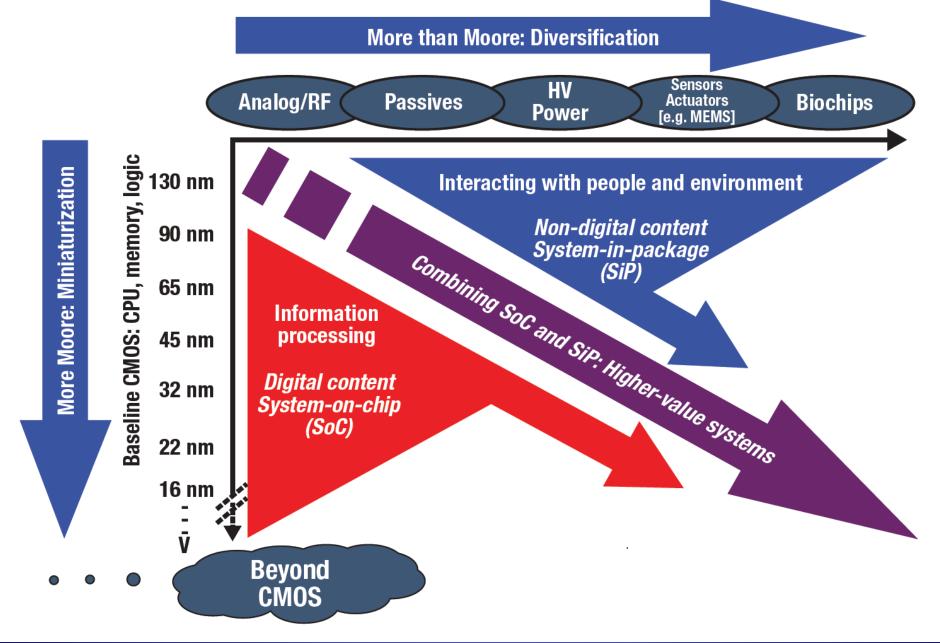

#### **More than Moore**

# How could near future ASIC looks like? (2 of 3)

- Standardization in use of both pure CMOS technology processes (180-130 nm for Analog part and 65 nm for Digital one) and community shared re-usable building block libraries

- Integration scale for ASICs (typ.) 32-128 channels per chip, built-in FEE ADC

- Highly integrated very sensitive analog (where possible differential) front-end

- Digitization (8-10 bit resolution typ.) at earliest stage at less than 1V power supply headroom

- Signal processing mostly in digital domain (DSP)

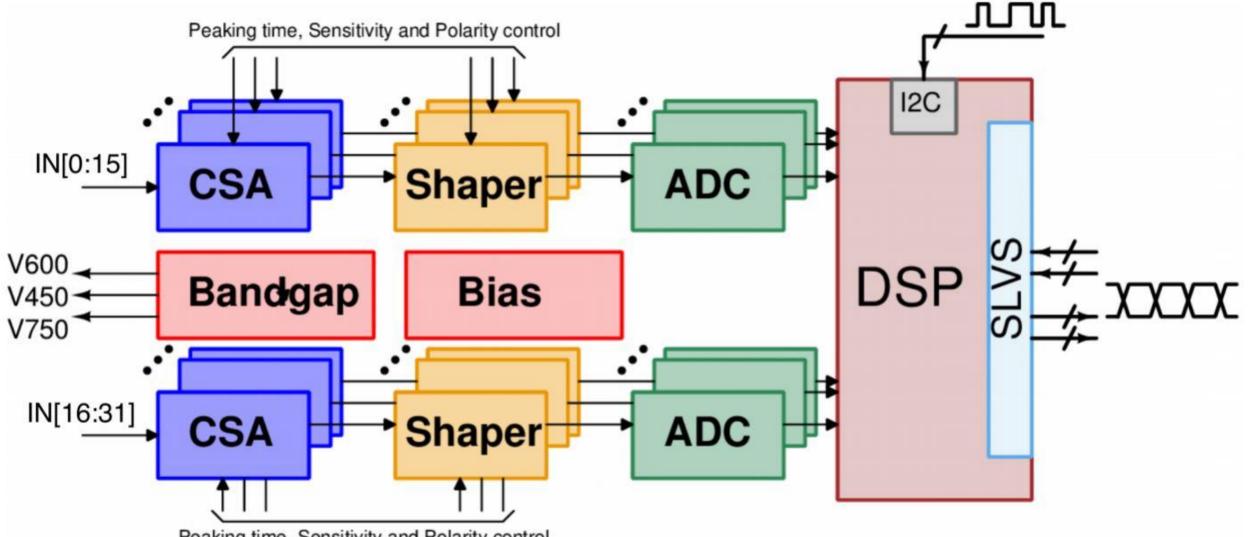

## Example ASIC 1 – SAMPA (ALICE project)

Peaking time, Sensitivity and Polarity control

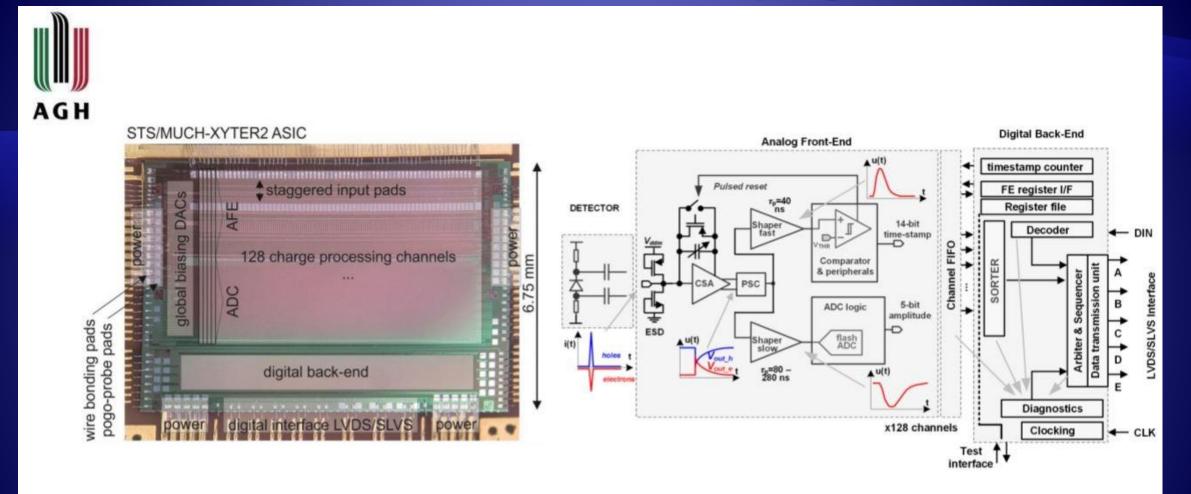

#### Example ASIC 2 (CBM project)

128 channels + 2 test channels

charge sensitive amplifier (continuous+pulsed reset, switchable gains (STS/MUCH) + trim)

5-bit amplitude measurement (shaper slow + ADC)

14-bit timestamp measurement (shaper fast + leading edge discriminator)

# How could near future ASIC looks like? (3 of 3)

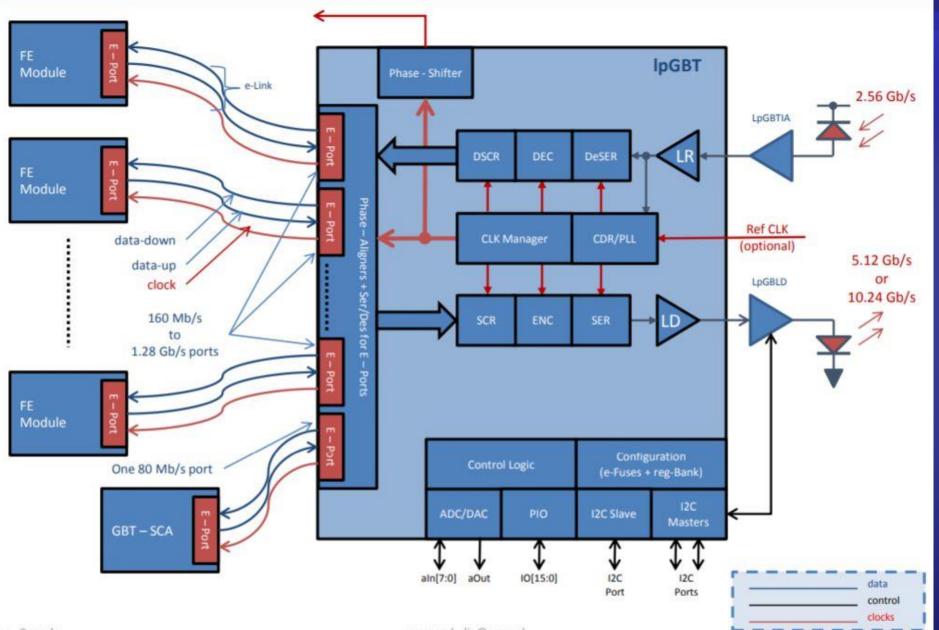

- High data rates via output (preferably optical) serial interfaces with speed in multi-Gbps range (10 Gbps under design)

- Big data processing (for ex. CMS detector raw data >1000 Pbyte/day (1 Mbyte x 40 MHz)) starting on detector

- Chips will not be cheaper than before

- Very difficult environment on TID (up to 100 Mrad) and high magnetic field (ex. few Tesla)

#### IpGBT: High Speed SerDes

CERN) at (common project m Example ASIC

12

szymon.kulis@cern.ch

# The Different Ages of Scaling (Different methods for different times) Geometrical Scaling (1975-2002) Reduction of horizontal and vertical physical dimensions in conjunction with improved performance of planar transistors

## ② Equivalent Scaling (2003~2024)

Reduction of only horizontal dimensions in conjunction with introduction of new materials and new physical effects. New vertical structures replace the planar transistor

# 3 3D Power Scaling (2025~2040)

Transition to complete vertical device structures. Heterogeneous integration in conjunction with reduced power consumption become the technology drivers .Gargin

### Conclusions

ASICs are of the key elements of future of detector setups due to new challenges in integration scale

Available commercial **processes** today are well ahead of most requirements (including radiation hardness) foreseen for particle and astrophysics` installations

Today an optimum choice of CMOS technology node (in terms of functionality over cost) is between **130-180 nm for analog** designs to **65 nm for digital** ones

Almost all ASICs are **mixed-signal** ones

The solution of **system** (architectural, structural) problems will demand substantially higher efforts to create not separate components, but whole systems on chip (**SoC**)

## Conclusions (2)

The **"Rad-hard by design"** approach for commercial CMOS technology is considered to be the best way of providing an **acceptable** radiation tolerance by circuital and layout techniques.

For radiation tolerance and temperature stability of the chips it is important to refine the existing libraries and design routes

The necessity of **much stronger collaboration** and coordination between all participants, sharing: the process of preparing human resources; the cost of expensive CAD and chip prototyping as well as steady updating design competences

# References

- M. Campbell Present and future of microelectronics Annual Meeting of the Future Circular Collider Study 9-13 April 2018, Amsterdam, fcc.web.cern.ch

- A. Marchioro How can Moore's Law help making better detectors? VCI February 2016

- E. Heijne Report on IEEE-ISSCC 2018: micro-nano-pico, we must go on. CERN Seminar, 13 March 2018 <u>https://indico.cern.ch/event/709523/</u>

- P.Gargini Roadmap Evolution: From NTRS to ITRS, From ITRS 2.0 to IRDS. October 2017 <u>https://e3s-center.berkeley.edu/wp-content/uploads/2017/12/1-1-1\_Gargini.pdf</u>

- International Roadmap for Devices and Systems (IRDS) <u>https://irds.ieee.org</u>

- R. Ballabriga et al. Asic developments for radiation imaging applications: The medipix and timepix family. NIM A 878, 10-23, 2018

- M. Bregant et al. SAMPA Chip: the New 32 Channels ASIC for the ALICE TPC and MCH Upgrades. JINST 12(04)C04008, April 2017

- R. SzczygieŁ et al. STS-XYTER, a 128 channel readout ASIC for silicon strips. FEE 20-25 May 2018 <u>https://indico.cern.ch/event/688153/contributions/2964664/attachments/1656161/2651261/2018.05.</u> <u>25 - FEE Kasinski v3.pdf</u>

- S. Kulis lpGBT design and status. FEE 20-25 May 2018 <u>https://indico.cern.ch/event/688153/contributions/2964670/attachments/1653896/2646608/fee2018</u> <u>kulis\_lpgbt.pdf</u>